Research

Co-processing on the cloud

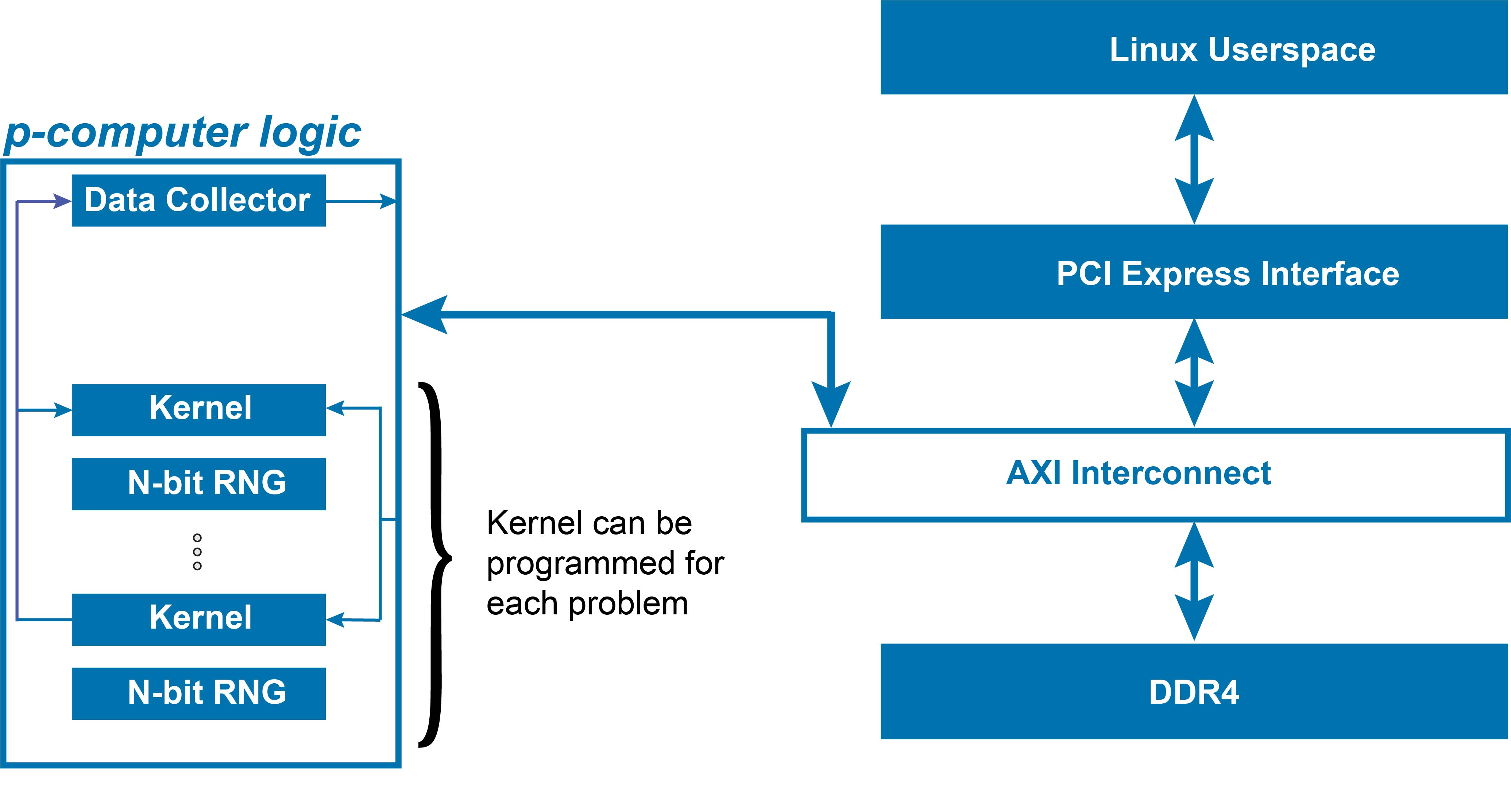

Due to the slowing down of Moore's law, domain-specific accelerators are the only way forward to decrease the energy consumption of desired operations and stay in the power budget. Here, AWS cloud FPGAs were utilized to accelerate applications in the deep learning and optimization field by mapping algorithms to hardware designs with high energy efficiency.

Hardware for AI

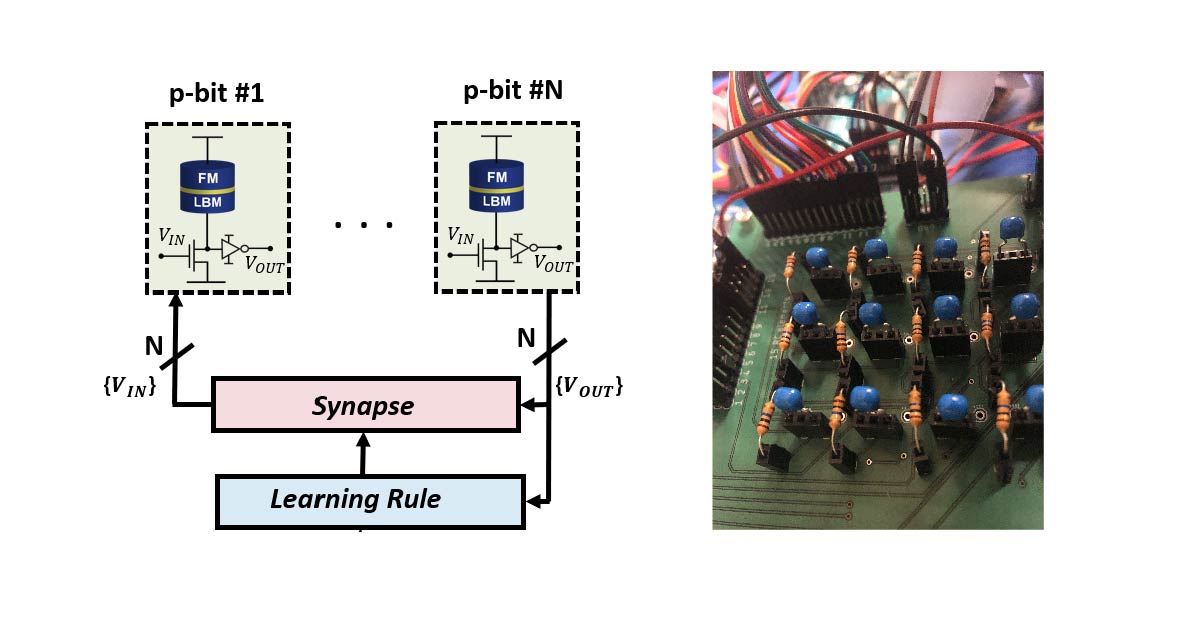

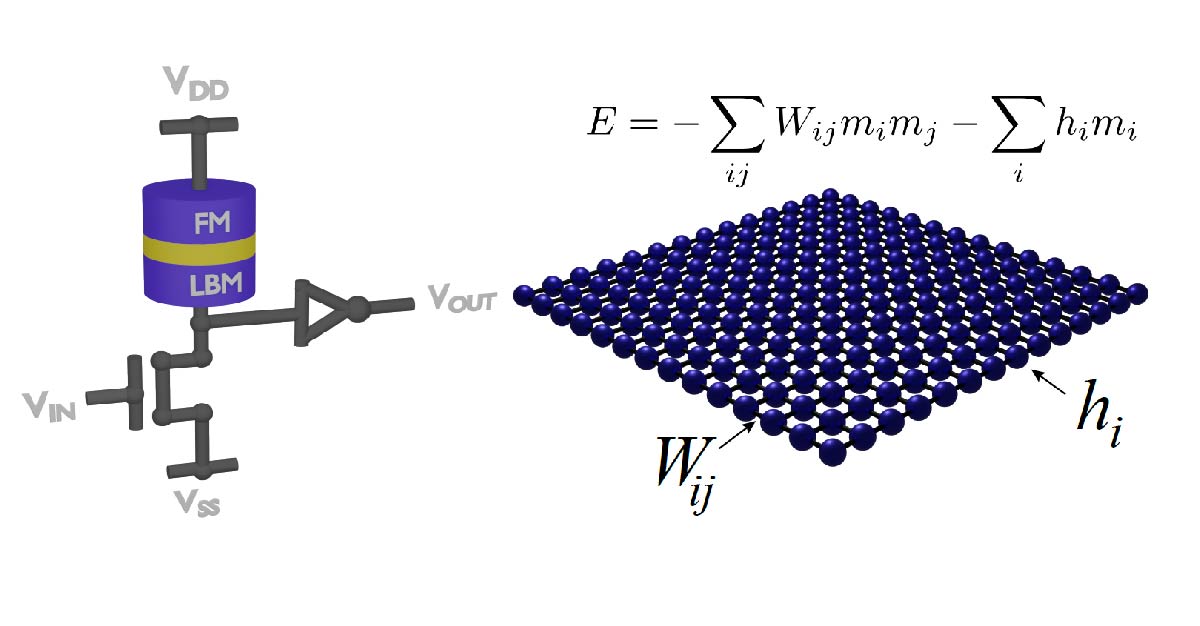

We demonstrated by experiment and simulation how a probabilistic circuit can learn different functionalities. Non-ideal characteristics in stochastic magnetic tunnel junctions can be countered by hardware-aware in-situ learning — an approach that should make it possible to scale p-computers up to GB scales by adjusting connectivity to match custom hardware characteristics.

Related Talk @ Physical Review Journal Club

Probabilistic computing

Novel beyond-Moore approaches are needed to increase computing performance. Probabilistic computing based on spintronic hardware makes it possible to efficiently process uncertainties inherent in data or leverage randomness to interpret, infer, and make better decisions faster.

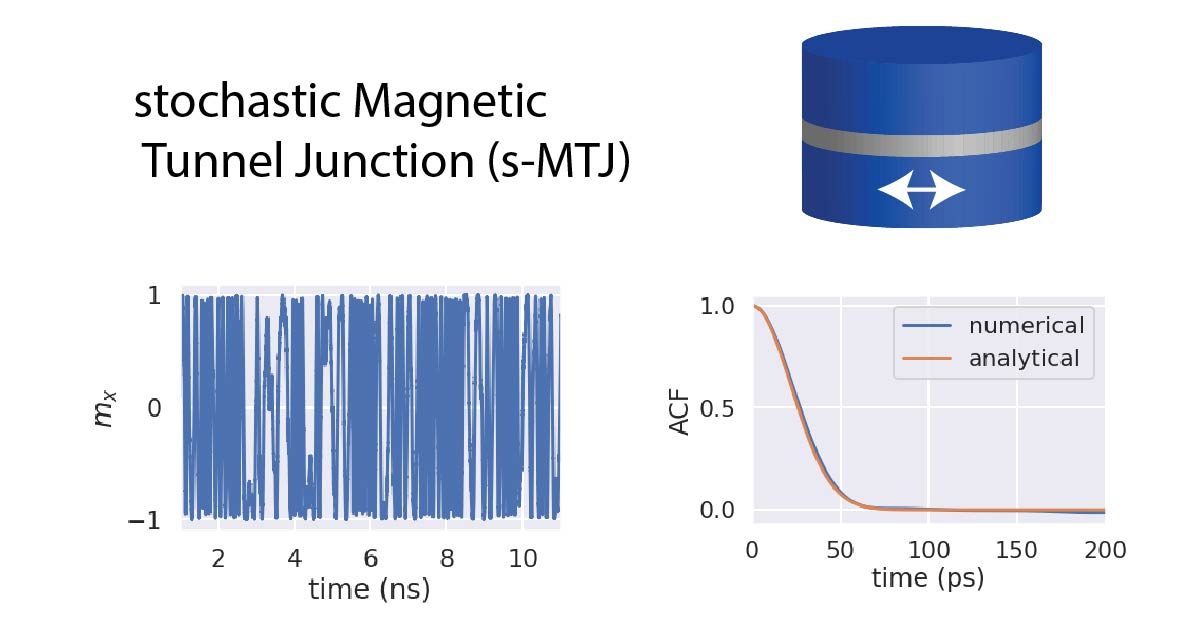

Thermal fluctuations in low-barrier nanomagnets

We discovered that specially designed nanomagnets can change states extremely quickly — in less than a billionth of a second — even at room temperature. These fast fluctuations are useful for probabilistic computing and hardware accelerators for Monte Carlo simulations. The prediction was later verified experimentally by independent groups at IBM and Tohoku University.

Code on GitHub

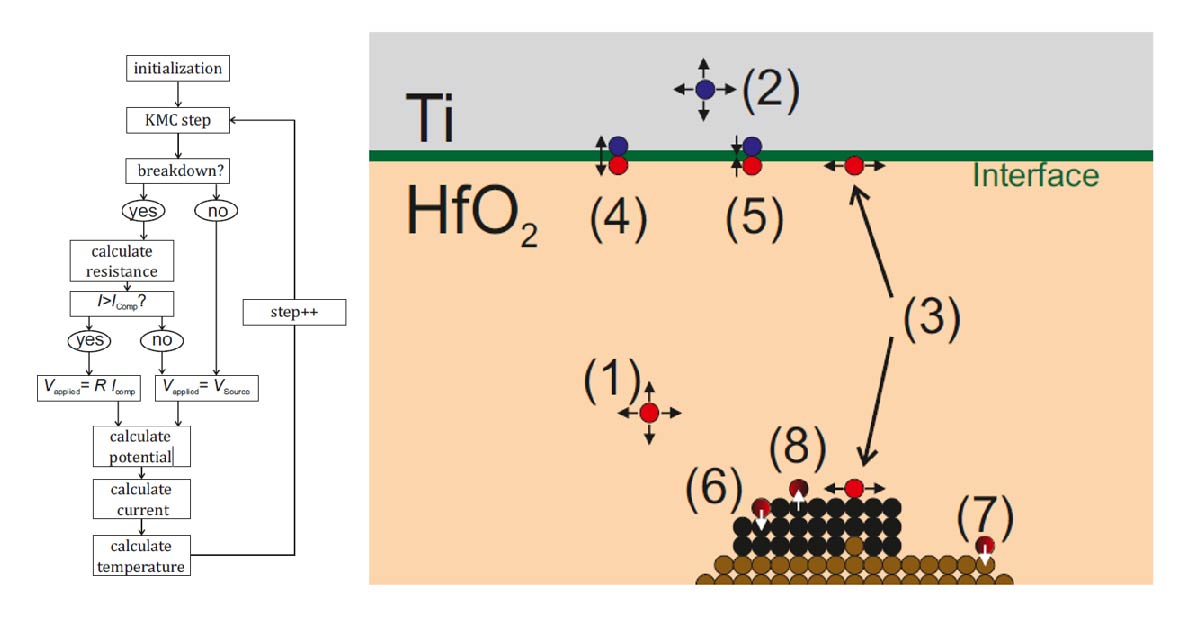

Exploring memristive nanostructures

Memristive devices play a vital role in in-memory computing and neuromorphic systems. We used Kinetic Monte Carlo simulations to understand how these devices form tiny conductive filaments at the nanoscale, providing valuable insights into the behavior of HfO₂ memristors and their potential for future technology.

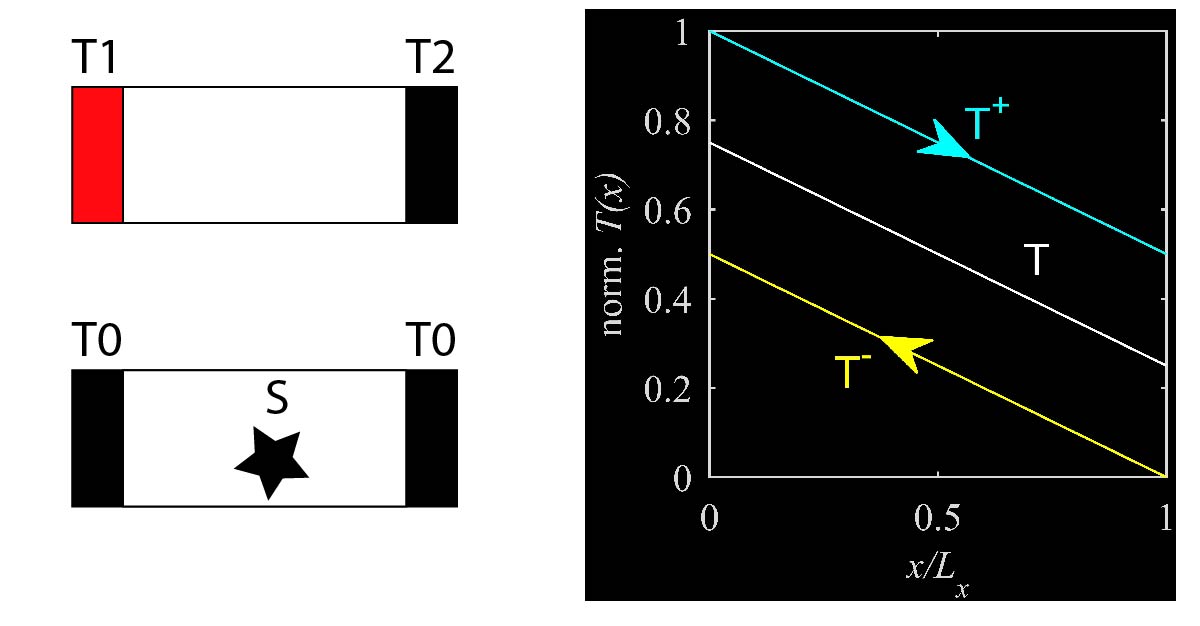

Thermal transport: ballistic to diffusive

Heat management is a critical challenge in developing smaller, more powerful chips. Using McKelvey-Shockley equations, we explored how heat moves at the nanoscale and showed how traditional heat-flow models can be adapted to work across different heat-transfer regimes — bridging the gap between theory and practical chip design.